Product Summary

? Bus Matrix

– Six 32-bit-layer Matrix

– Boot Mode Select Option, Remap Command

? Fully-featured System Controller, including

– Reset Controller, Shutdown Controller

– Four 32-bit Battery Backup Registers for a Total of 16 Bytes

– Clock Generator and Power Management Controller

– Advanced Interrupt Controller and Debug Unit

– Periodic Interval Timer, Watchdog Timer and Real-time Timer

? Reset Controller (RSTC)

– Based on a Power-on Reset Cell, Reset Source Identification and Reset Output

Control

? Clock Generator (CKGR)

– Selectable 32,768 Hz Low-power Oscillator or Internal Low Power RC Oscillator on

Battery Backup Power Supply, Providing a Permanent Slow Clock

– 3 to 20 MHz On-chip Oscillator, One up to 800 MHz PLL and One up to 100 MHz PLL

? Power Management Controller (PMC)

– Very Slow Clock Operating Mode, Softw are Programmable Power Optimization

Capabilities

–

Parametrics

– Mode for General Purpose 2-wire UART Serial Communication

Periodic Interval Timer (PIT)

– 20-bit Interval Timer plus 12-bit Interval Counter

Watchdog Timer (WDT)

– Key-protected, Programmable Only Once, Window ed 16-bit Counter Running at Slow Clock

Real-time Timer (RTT)

– 32-bit Free-running Backup Counter Runn ing at Slow Clock with 16-bit Prescaler

One 4-channel 10-bit Analog-to-Digital Converter

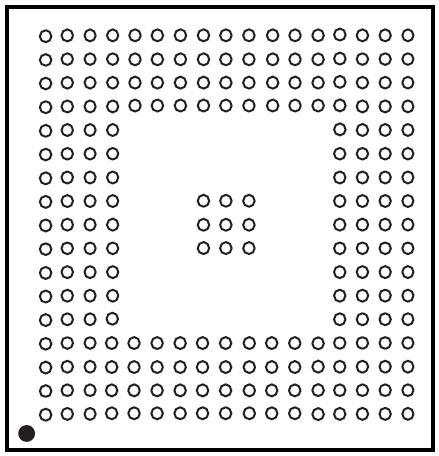

Three 32-bit Parallel Input/Output Controllers (PIOA, PIOB, PIOC)

– 96 Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os

– Input Change Interrupt Capability on Each I/O Line

– Individually Programmable Open-drain, Pull-up Resistor and Synchronous Output

– All I/O Lines are Schmitt Trigger Inputs

Peripheral DMA Controller Channels (PDC)

One Two-slot MultiMedia Card Interface (MCI)

– SDCard/SDIO and MultiMediaCard

?

Compliant

– Automatic Protocol Control and Fast Automatic Data Transfers with PDC

One Synchronous Serial Controller (SSC)

– Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

– I2S Analog Interface Support, Time Division Multiplex Support

– High-speed Continuous Data Stream Ca pabilities with 32-bit Data Transfer

Four Universal Synchron ous/Asynchronous Receiver Transmitters (USART)

– Individual Baud Rate Generator, IrDA

?

Infrared Modulation/Demodulatio n, Manchester Encoding/Deco

– Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

– Full Modem Signal Control on USART0

Two 2-wire UARTs

Two Master/Slave Serial Peripheral Interfaces (SPI)

Features

The AT91SAM9G20 is based on the integration of an ARM926EJ-S processor with fast ROM

and RAM memories and a wide range of peripherals.

The AT91SAM9G20 embeds an Ethernet MAC, one USB Device Port, and a USB Host control-

ler. It also integrates severa l standard peripherals, such as the USART, SPI, TWI, Timer

Counters, Synchronous Serial Controller, ADC and MultiMedia Card Interface.

The AT91SAM9G20 is architectured on a 6-layer matrix, allowing a maximum internal bandwidth

of six 32-bit buses. It also features an External Bus Interface capable of interfacing with a wide

range of memory devices.

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

AT91SAM9G20B-CFU |

Atmel |

ARM Microcontrollers (MCU) MRL B; 64K ROM 2x16K SRAM |

Data Sheet |

|

|

||||||||||||

|

AT91SAM9G20B-CU |

Atmel |

ARM Microcontrollers (MCU) 2x16K SRAM Ethernet USB Host Bus Intrfc |

Data Sheet |

|

|

||||||||||||

|

AT91SAM9G20-EK |

Atmel |

Development Boards & Kits - ARM 32-bit MCU Eval Kit |

Data Sheet |

|

|

||||||||||||

|

AT91SAM9G20B-CU-999 |

Atmel |

ARM Microcontrollers (MCU) . - BGA,GREEN,IND TEMP, T&R,MRLB |

Data Sheet |

|

|

||||||||||||

|

AT91SAM9G20-CU |

Atmel |

ARM Microcontrollers (MCU) 32-bit |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))