Product Summary

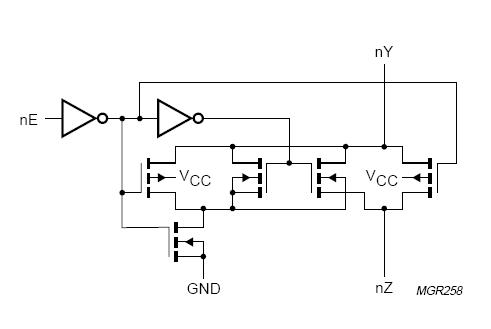

The 74HC4046AD is a high-speed Si-gate CMOS device and is pin compatible with the “4066” of the “4000B” series. The 74HC4046AD is specified in compliance with JEDEC standard no. 7A. The 74HC4046AD has four independent analog switches. Each switch has two input/output terminals (nY, nZ) and an active HIGH enable input (nE). When nE is LOW the belonging analog switch is turned off.

Parametrics

74HC4046AD absolute maximum ratings: (1) turn-on time nE to Vos (CL=15pF; RL=1kW; VCC=5V): 11ns for HC, 12ns for HCT; (2) turn-off time nE to Vos: 13ns for HC, 16ns for HCT; (3) input capacitance: 3.5pF; (4) power dissipation capacitance per switch: 11pF for HC, 12pF for HCT; (5) max. Switch capacitance: 8pF.

Features

74HC4046AD features: (1) Very low “ON” resistance; (2)50Ω (typ.) at VCC = 4.5V; (3)45Ω (typ.) at VCC = 6.0V; (4)35Ω (typ.) at VCC = 9.0V; (5) Output capability: non-standard; (6) ICC category: SSI.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HC4046AD |

NXP Semiconductors |

Phase Locked Loops (PLL) PHASE LOCKED LOOP W/VCO |

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC4046AD,652 |

NXP Semiconductors |

Phase Locked Loops (PLL) PHASE LOCKED LOOP |

Data Sheet |

|

|

||||||||||||

|

74HC4046AD,653 |

NXP Semiconductors |

Phase Locked Loops (PLL) PHASE LOCKED LOOP W/VCO |

Data Sheet |

|

|

||||||||||||

|

74HC4046ADB,118 |

NXP Semiconductors |

Phase Locked Loops (PLL) PHASE LOCKED LOOP |

Data Sheet |

|

|

||||||||||||

|

74HC4046ADB,112 |

NXP Semiconductors |

Phase Locked Loops (PLL) PHASE LOCKED LOOP |

Data Sheet |

|

|

||||||||||||

|

74HC4046ADB |

NXP Semiconductors |

Phase Locked Loops (PLL) PHASE LOCKED LOOP W/VCO |

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC4046ADB-T |

NXP Semiconductors |

Phase Locked Loops (PLL) PHASE LOCKED LOOP W/VCO |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))